Introductory and Advanced Topics on P4 Programmable Data Plane Switches

Elie Kfoury, Ali AlSabeh University of South Carolina http://ce.sc.edu/cyberinfra ekfoury@email.sc.edu, aalsabeh@email.sc.edu

WASTC 2022 virtual Faculty Development Weeks (vFDW) June 13, 2022

## P4 Program Building Blocks

Lab activities are described in Lab 3, P4 Programmable Data Plane Switches (BMv2) lab series

## V1Model

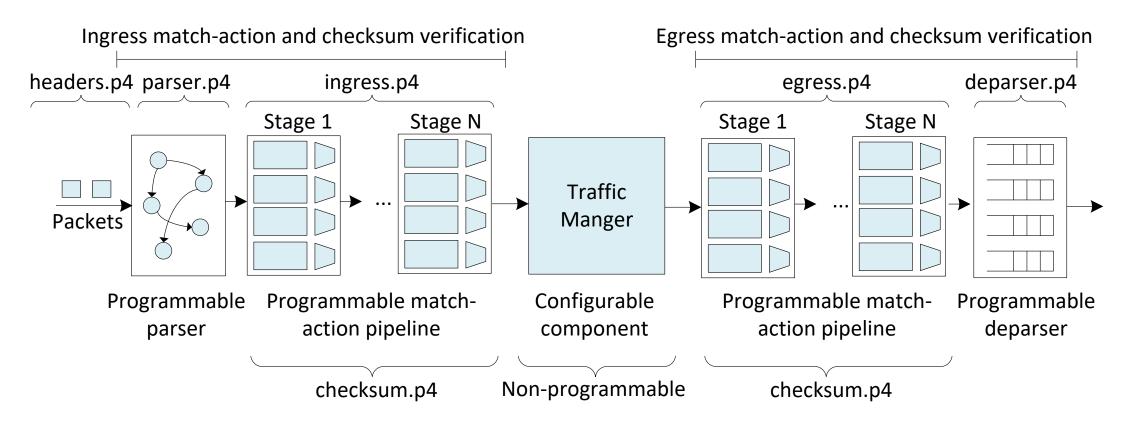

- Common P4<sub>16</sub> architecture used with BMv2

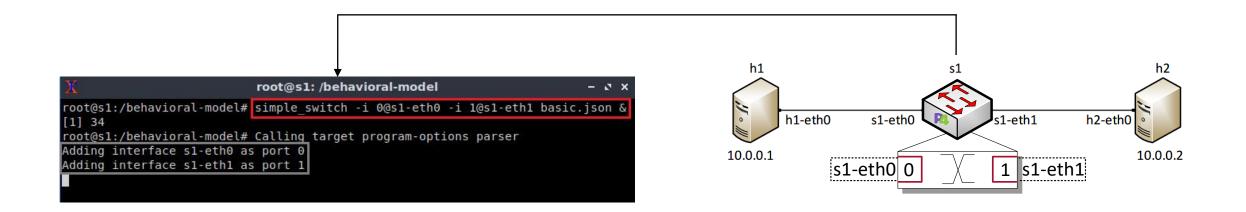

- Implemented on top of BMv2's simple\_switch target

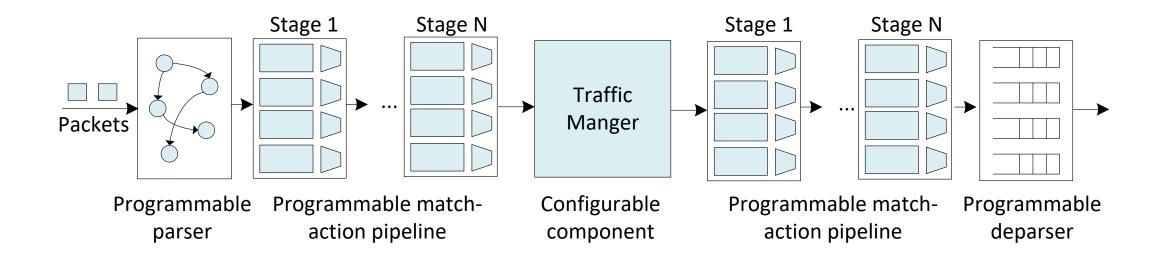

- It consists of a programmable parser, an ingress match action pipeline, a traffic manager, an egress match-action pipeline, and a deparser

## V1Model

- Common P4<sub>16</sub> architecture used with BMv2

- Implemented on top of BMv2's simple\_switch target

## Lab Topology and Objectives

- The topology consists of two hosts: h1 and h2; one P4 switch: s1

- Mapping the P4 program components to the components of the programmable pipeline

- Trace the lifecycle of a packet as it traverses the pipeline