#### Registers, Packet Digests

Jorge Crichigno<sup>1</sup>, Mariam Kiran<sup>2</sup> <sup>1</sup>University of South Carolina, <sup>2</sup>ESnet

Lab Assistants: Elie Kfoury, Ali AlSabeh, Jose Gomez University of South Carolina

WASTC 2022 virtual Faculty Development Weeks (vFDW) June 17, 2022

- Registers are stateful memories whose values can be read and written in actions in the data plane

- They can also be read and written by the control plane

- They are more general than counters; arbitrary data can be stored in registers

- Registers are global memory resources; any match-action tables can reference to them

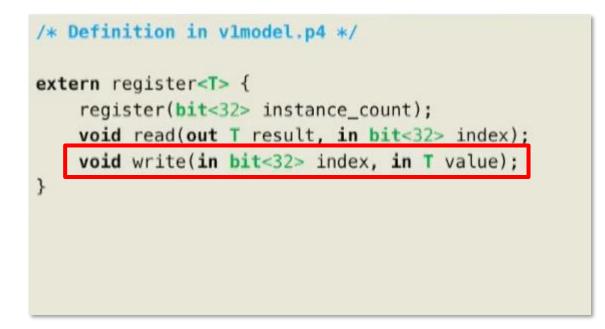

• The definition of the V1 Model register includes

> register instantiation that receives an input parameter -number of elements of the register

```

/* Definition in vlmodel.p4 */

extern register<T> {

register(bit<32> instance_count);

void read(out T result, in bit<32> index);

void write(in bit<32> index, in T value);

}

```

1. V. Gurevich, Introduction to P416. Online: https://tinyurl.com/2h93pnyd

- The definition of the V1 Model register includes

- > register instantiation that receives an input parameter -number of elements of the register

- read method that receives an output parameter –where to store the register value– and an input parameter –index

```

/* Definition in vlmodel.p4 */

extern register<T> {

register(bit<32> instance count):

void read(out T result, in bit<32> index);

void write(in bit<32> index, in T value);

}

```

1. V. Gurevich, Introduction to P416. Online: https://tinyurl.com/2h93pnyd

- The definition of the V1 Model register includes

- > register instantiation that receives an input parameter -number of elements of the register

- read method that receives an output parameter –where to store the register value– and an input parameter –index

- > write method that receives two input parameters, index and value to store in the register

1. V. Gurevich, Introduction to P416. Online: https://tinyurl.com/2h93pnyd

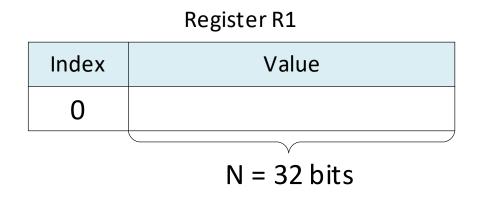

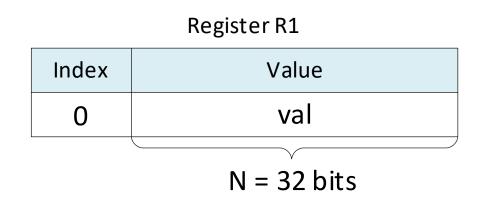

## Instantiating a Single Element Register

• The syntax below shows how to instantiate a single element register in P4

register<bit<N>>(1) R1;

• Register R1 contains a single N-bit element

## Writing a Single Element Register

• The syntax below shows how to write (store) a value val in register R1, element 0

R1.write(0,val)

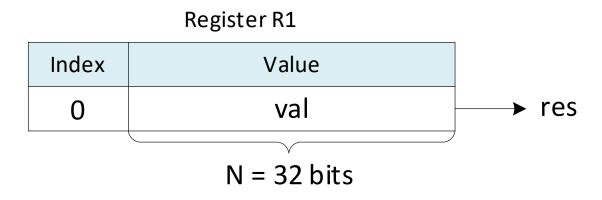

# Reading a Single Element Register

• The syntax below shows how to read the value stored in element 0 of the register, and store it into the variable res

R1.read(res,0)

• Note that the value val is stored in the variable res

Example: computing the time between two consecutive packets of a flow (inter-packet gap)

| Code                                                                                        | Standard metadata                                                                                  |

|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| <pre>register<bit<48>&gt;(16384) last_seen;</bit<48></pre>                                  | <pre>struct standard_metadata_t {     bit&lt;9&gt; ingress_port;</pre>                             |

| <pre>action get_inter_packet_gap(out bit&lt;48&gt; interval, bit&lt;32&gt; flow_id) {</pre> | <pre>bit&lt;9&gt; egress_spec;<br/>bit&lt;9&gt; egress_port;<br/>bit&lt;32&gt; clone_spec;</pre>   |

| <pre>bit&lt;48&gt; last_pkt_ts;</pre>                                                       | <pre>bit&lt;32&gt; instance_type;<br/>bit&lt;1&gt; drop;<br/>bit&lt;16&gt; recirculate_port;</pre> |

| /* Get the time the previous packet was seen */                                             | <pre>bit&lt;32&gt; packet_length;</pre>                                                            |

| <pre>last_seen.read(last_pkt_ts, flow_id);</pre>                                            | <pre>bit&lt;32&gt; enq_timestamp;<br/>bit&lt;19&gt; enq_qdepth;</pre>                              |

| /* Calculate the time interval */                                                           | <pre>bit&lt;32&gt; deq_timedelta; bit&lt;19&gt; deq_depth;</pre>                                   |

| <pre>interval = standard_metadata.ingress_global_timestamp - last_pkt_ts;</pre>             | <pre>bit&lt;48&gt; ingress global timestamp;<br/>bit&lt;32&gt; lf_field_list;</pre>                |

| /* Update the register with the new timestamp */                                            | <pre>bit&lt;16&gt; mcast_grp;<br/>bit&lt;1&gt; resubmit_flag;</pre>                                |

| <pre>last_seen.write(flow_id, standard_metadata.ingress_global_timestamp);</pre>            | <pre>bit&lt;16&gt; egress_rid;<br/>bit&lt;1&gt; checksum_error;<br/>}</pre>                        |

| }                                                                                           |                                                                                                    |

# Atomicity

- Hardware and software targets use atomic operations on P4 stateful objects

- For Intel Tofino switch (Vladimir Gurevich)<sup>1</sup>:

In case of stateful objects, a complex read-modify-write operation counts as one access and is performed by a special ALU (counter ALU, meter ALU, stateful ALU, etc.)

Since this counts as one operation, it is atomic for all practical intents and purposes. For example, it is impossible to see a stateful object in some "intermediate" state. Similarly, when the same object (instance) is accessed by the next packet, it does see it fully modified.

#### • For BMv2 v1model implementation<sup>2</sup>:

The BMv2 v1model implementation supports parallel execution. It uses locking of all register objects accessed within an action to guarantee that the execution of all steps within an action are atomic, relative to other packets executing the same action, or any action that accesses some of the same register objects.

- 1. Intel<sup>®</sup> Connectivity Research Program (Private). Memory semantics of Tofino architecture. Online: <u>https://tinyurl.com/yz7hzydr</u>

- 2. P4Lang Consortium, The BMv2 Simple Switch target. Online: https://tinyurl.com/26b762m3

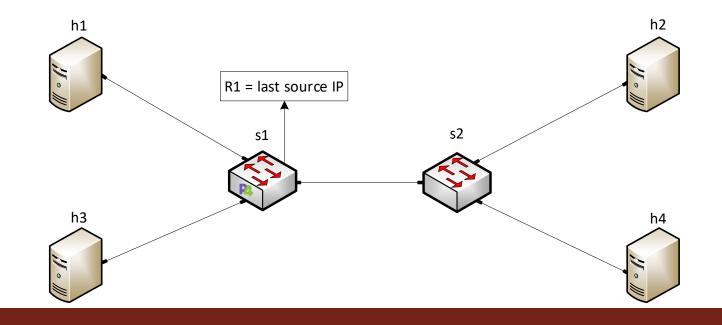

# Lab 9 Topology and Objectives

- This lab requires the learner to write a P4 program that stores the last observed source IP address into a register

- The topology consists of four hosts, one P4 switch, and one legacy switch

- The objectives are

- Be able to write P4 programs using registers

- > Read, write, and reset registers from the control plane

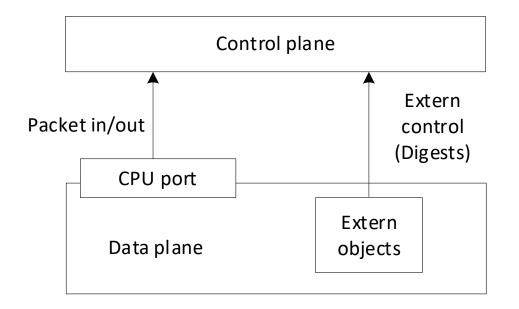

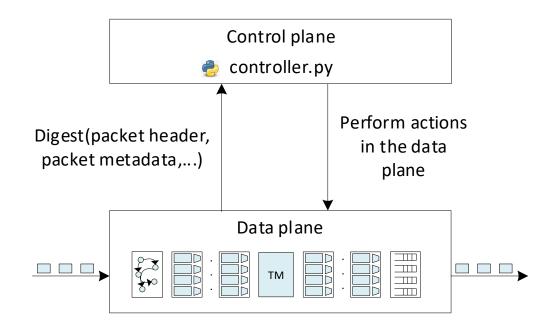

## Data Plane to Control Plane Communication

- The data plane can send a packet to the control plane via a particular port reserve for this purpose

- Another mechanism for the data plane to communication with the control plane is packet digest

## **Packet Digests**

- The contents of a digest for one packet are typically much smaller than the packet

E.g., packet header/s and/or metadata to be processed by a program in the control plane

- The controller computes digests and communicates with the data plane using runtime APIs

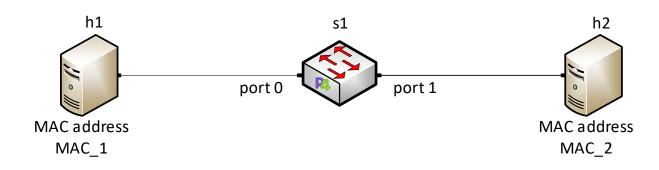

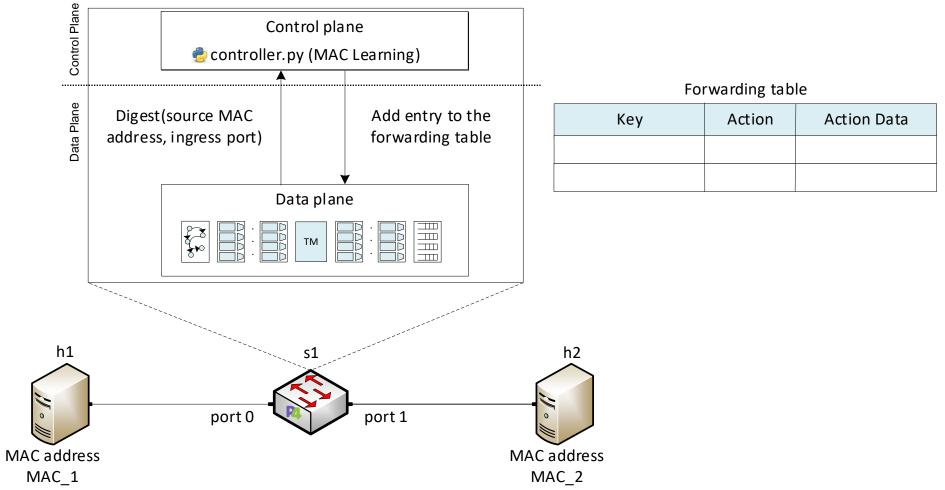

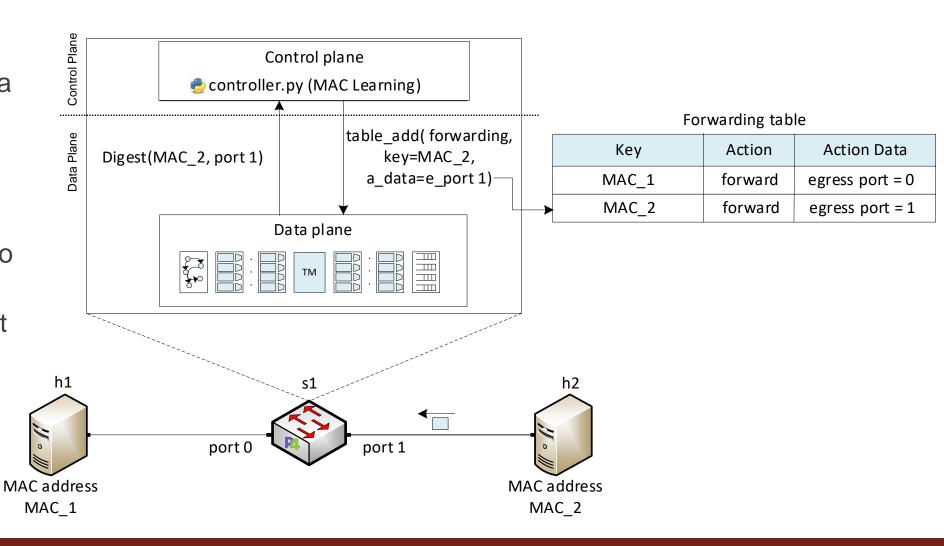

# Lab Scenario: MAC Learning

Initially the forwarding table is empty

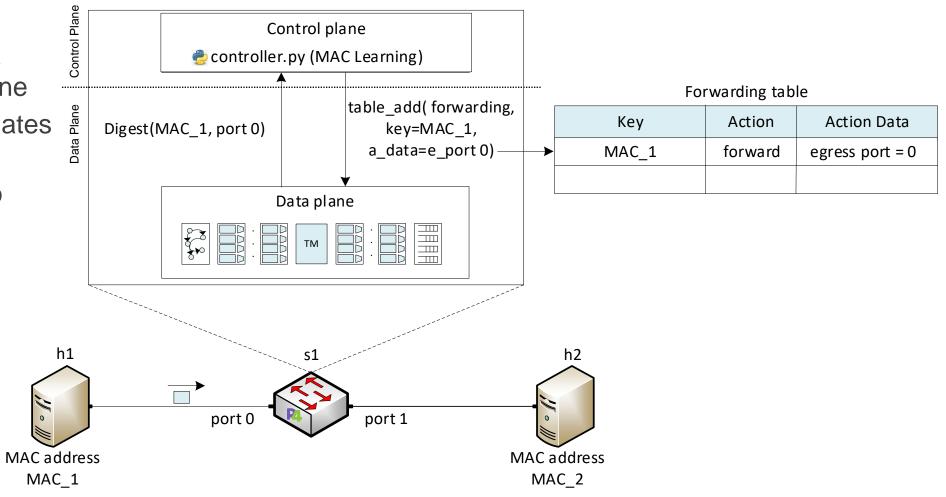

# Lab Scenario: MAC Learning

- Switch s1 receives a packet from host h1

- The data plane sends a digest to the control plane

- The control plane populates the forwarding table

- Switch s1 learns how to reach host h1

# Lab Scenario: MAC Learning

- Switch s1 receives a packet from host h2

- The data plane sends a digest to the control plane

- The control plane populates the table

- Switch s1 learns how to reach host h2

- Host h1 can reach host h2

# Lab 11 Topology and Objectives

- The topology consists of two hosts: h1, h2, and one P4 switch: s1

- The objectives are

- Creating a digest with the source MAC address and ingress port

- Sending the digest to the control plane

- > Programming a controller with the runtime APIs to create table entries

- Populating the forwarding table from the control plane

- Verifying the connectivity between end hosts