Elie Kfoury

Assistant Professor, Integrated Information Technology Department

Elie Kfoury, Assistant Professor, Integrated Information Technology, College of Engineering and Computing.

Elie Kfoury received the Ph.D. degree in Informatics from the University of South Carolina (USC), in 2023. He is currently an assistant professor in the Integrated Information Technology department at USC. As a member of the Cyberinfrastructure Laboratory, he developed training materials using virtual labs on high-speed networks, TCP congestion control, programmable switches, SDN, and cybersecurity. He is the co-author a book “High-Speed Networks: A Tutorial”, that is being used nationally for deploying, troubleshooting, and tuning Science DMZ networks. His research interests include P4 programmable data planes, computer networks, cybersecurity, and Blockchain. He previously worked as a research and teaching assistant in the computer science department at the American University of Science and Technology in Beirut.

Contact

Office Location

Innovation Center

550 Assembly Street, Suite 1300

Office 1307

Columbia, SC 29208

Email

ekfoury@email.sc.edu

Phone

803-201-5308Research Interests

Traditionally, the data plane has been designed with fixed functions to forward packets using a small set of protocols (e.g., IP, Ethernet). This closed-design paradigm has limited the capability of the switches to proprietary implementations which are hard-coded by vendors. Recently, data plane programmability has attracted significant attention from both the research community and the industry, permitting programmers to run customized packet processing functions in the data plane. This open-design paradigm is paving the way for an unprecedented wave of innovation and experimentation by reducing the time of designing, testing, and adopting new protocols; enabling a customized, top-down approach to develop network applications; providing granular visibility of packet events defined by the programmer; reducing complexity and enhancing resource utilization of the programmable switches; and drastically improving the performance of applications that are offloaded to the data plane

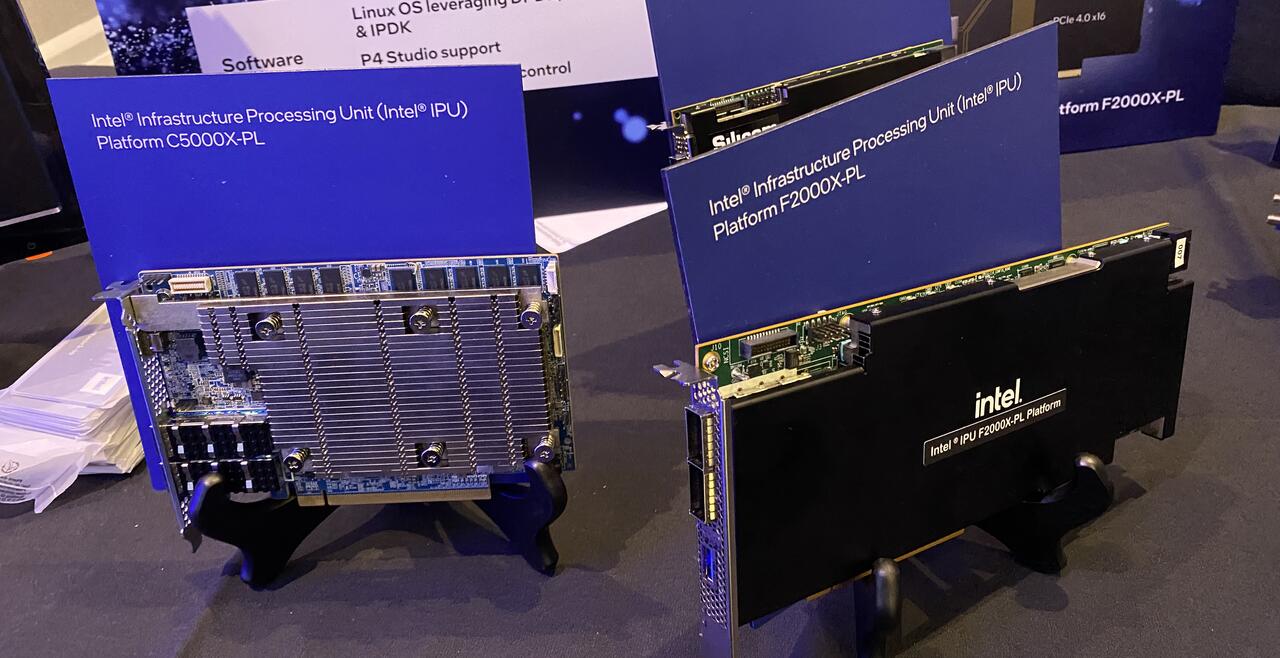

The end of Moore's Law and Dennard Scaling has slowed processor improvements in the past decade. While multi-core processors have improved performance, they are limited by the application's level of parallelism, as prescribed by Amdahl's Law. This has led to the emergence of domain-specific processors that specialize in a narrow range of functions. Smart Network Interface Cards (SmartNICs) can be seen as an evolutionary technology that combines heterogeneous domain-specific processors and general-purpose cores to offload infrastructure tasks.

With the proliferation of high-speed networks, there is a pressing need to revisit the conventional TCP congestion control mechanisms that were primarily designed for slower networks. The challenge here is to optimize data transfer and resource utilization in high-speed environments while ensuring fairness and efficient congestion management. This area of research involves the exploration of novel TCP congestion control algorithms (e.g., BBR), network-assisted congestion feedback, network tuning (e.g., Science DMZ), network measurements (e.g., P4-based passive measurements, perfSONAR).