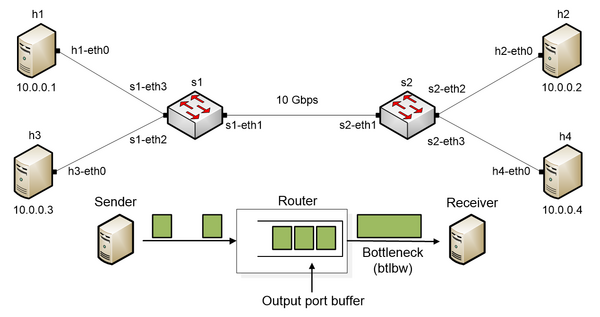

The Cyberinfrastructure Lab at the University of South Carolina (CI Lab @ USC) is a virtual platform deployed for cybertraining purposes. Current training labs include network tools and protocols (e.g., Mininet, Netem, TCP congestion control), perfSONAR, Zeek / Bro, and others.

To access the virtual laboratory:

1. Fill out the form requesting access to CI Lab [form] (you will receive a username and password within 24 hours).

2. For any issues accessing your Netlab account, feel free to contact choueiri@email.sc.edu.

3. Access the CI Lab at https://netlab.cec.sc.edu. For a CI Lab user guide, click here [PDF].

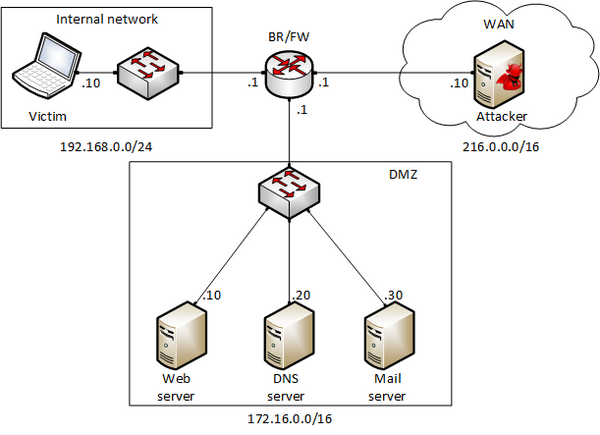

Introduction to Intrusion Detection Using Zeek

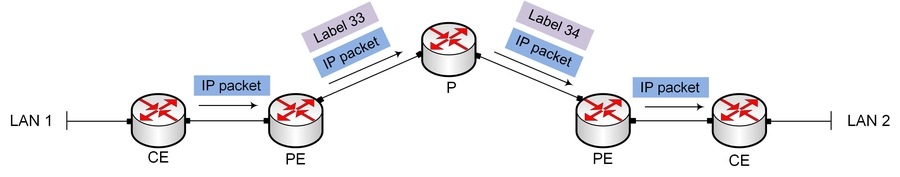

This lab series equips learners with the skills to detect and analyze both Layer 2 and Layer 3 network attacks using the Zeek framework in an emulated environment. Through hands-on exercises, participants explore how to identify data link–layer threats such as ARP spoofing, DHCP starvation, and CAM table overflow, alongside network-layer attacks including DNS amplification, TCP SYN floods, and BGP hijacking. By leveraging Zeek’s event-driven scripting and custom logging capabilities, learners gain the ability to monitor traffic patterns, detect anomalies across multiple protocol layers, and develop comprehensive detection strategies that enhance network visibility and security across the full stack.

| Lab 1 | Introduction to CORE |

| Lab 2 | Introduction to Zeek |

| Lab 3 | Introduction to Zeek Scripting and Events |

| Lab 4 | Zeek Data Types and Custom Logging |

| Lab 5 | ARP Protocol Spoofing Detection |

| Lab 6 | DNS Amplification Detection |

| Lab Manuals | Introduction to Intrusion Detection Using Zeek [PDF] |

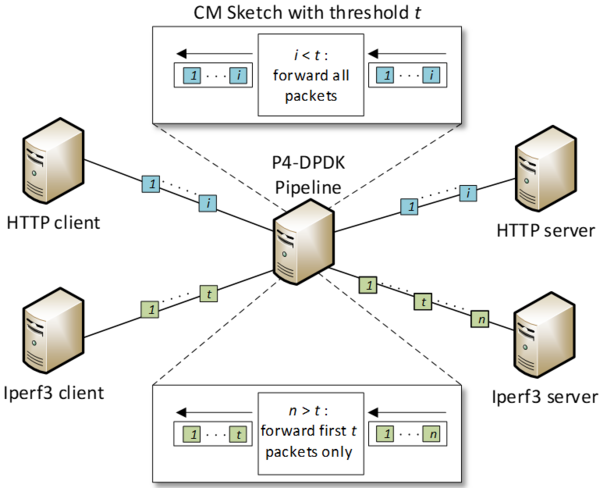

DPU Programming using P4

This lab series provides a comprehensive introduction to programmable data plane development on NVIDIA BlueField DPUs using the DOCA Pipeline Language (DPL), a P4 domain-specific language. Through a sequence of practical, hands-on exercises, the series guides learners from foundational concepts of P4 and DPL syntax to advanced data plane programming techniques on SmartNIC architectures. Participants will gain experience in defining custom headers and parsers, implementing packet mirroring and forwarding applications, configuring match-action tables, and managing runtime control through P4Runtime.

| Lab 1 | Introduction to P4 and DPL |

| Lab 2 | Implementing a Custom Header and Parser |

| Lab 3 | Implementing a Packet Mirroring Application |

| Lab 4 | Introduction to Match-action Tables |

| Lab 5 | Implementing Match-action Rules Using P4 Runtime |

| Lab 6 | Implementing Direct and Indirect Counters |

| Lab 7 | Performing Packet Statistics Monitoring using DOCA Nspect |

| Lab Manuals | DPU Programming using P4 Lab Series [PDF] |

DPU Programming using DOCA

This lab series provides an introduction to DPU programming using the NVIDIA DOCA framework. Through a sequence of hands-on labs, the lab series provides practical experience with DOCA APIs and infrastructure for accelerating data center applications on BlueField DPUs. The series covers DPU initialization, device and memory management, task execution using the DOCA progress engine, and the use of hardware accelerators for offloading compute-intensive functions.

| Lab 1 | Initializing and Configuring DOCA Environment |

| Lab 2 | Device Subsystem |

| Lab 3 | Memory Management |

| Lab 4 | Progress Engine and Execution Model |

| Lab 5 | Accelerator Invocation |

| Lab Manuals | DPU Programming using DOCA Lab Series [PDF] |